A CASCADED-IMPEDANCE-INVERTER MODEL OF WIDE-BAND FREQUENCY TRIPLEXERS\*

Jon C. Redd

Kenneth L. Kotzebue

Department of Electrical Engineering

University of California

Santa Barbara, California

Summary

A charge-storage diode frequency tripler can be modeled as two cascaded impedance inverters. This approach has been used to design and construct a tripler at 1.06 GHz input frequency with a measured midband efficiency of 50% and a 3 dB bandwidth of 38%.

It has been demonstrated recently<sup>1</sup> that it is possible to design and construct broadband frequency triplers of high efficiency using charge-storage diodes (experimentally 45% bandwidth, 70% midband efficiency at 100-MHz input frequency). The design procedure used is based on a computer analysis similar to that used by Burkhardt.<sup>2</sup> This method is an effective one; however, extensive computer time is required to complete a design. An alternative approach is to model the diode behavior by a cascade of two impedance inverters. While this approach is exact only under one set of operating conditions which can occur only at a single frequency, it is a much simpler approach which has been found to give results, over a wide range of frequencies, which are not greatly different from those obtained from the more involved computer analysis. (This approach is similar to the one recently developed for the design of wide-band doublers.<sup>3</sup>)

The basic tripler model used incorporates an ideal charge-storage diode with current flow allowed at the input frequency, output frequency, and second harmonic idler frequency.

The voltage-charge relationship for an ideal charge-storage diode is given by:

$$V(q) = qS_{\max} \quad q > 0 \\ = 0 \quad q \leq 0$$

where  $S_{\max}$  is the elastance of the reversed-biased diode. A constant resistance  $R_s$  is assumed to be in series with this piecewise linear elastance. The charge stored in the diode may be represented by:

$$q = q_0 + q_1 \cos(\omega t) + q_2 \cos(2\omega t + \theta_2) \\ + q_3 \cos(3\omega t + \theta_3) .$$

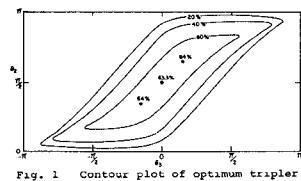

Using the computer, the optimum efficiency for a given  $q_0$ ,  $q_1$ ,  $\theta_2$ ,  $\theta_3$  and diode Q (Q defined as  $S_{\max}/R_s \omega$ ) can be found. It has been useful to plot this data as a contour plot of efficiency as a function of  $\theta_2$  and  $\theta_3$ . Such a contour plot is shown in Fig. 1 for  $q_0 = 0$  and a diode Q = 40. Note that efficiency is high along a straight line through the point  $\theta_2 = \pi/2$ ,  $\theta_3 = 0$ , with unity slope. (The center point along this high-efficiency "ridge",  $\theta_2 = \pi/2$ ,  $\theta_3 = 0$ , is the point used by Steinbrecher.<sup>4</sup>) Each point on the contour plot corresponds to a particular impedance at the first, second, and third harmonics. Wide-band operation can be achieved with no degradation in efficiency if multiplier network impedances can be synthesized which vary with frequency along the high-efficiency region of the contour plot.

The complete computer analysis shows that the optimum diode input and load resistances change rapidly in the neighborhood of  $\theta_2 = \pi/2$ ,  $\theta_3 = 0$ . Since abrupt changes in impedance levels are at best difficult to synthesize, the contour plot center point should occur near the end of the frequency range of operation. This is accomplished by resonating the idler circuit at the high end of the band rather than at midband.

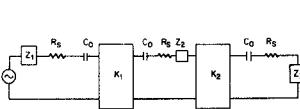

The ideal diode model reduces exactly to the impedance inverter structure in Fig. 2 at the ridge central point. The parameters in this circuit model are defined as:

$$K_1 = \frac{2}{3\pi} \frac{S_{\max}}{\omega} \quad K_2 = \frac{2}{5\pi} \frac{S_{\max}}{\omega}$$

$R_s$  = series resistance of diode.

$$C_0 = \frac{2}{S_{\max}}$$

$Z_1$  = 1st harmonic circuit impedance.

$Z_2$  = 2nd harmonic circuit impedance.

$Z_3$  = 3rd harmonic circuit impedance.

When the tripler operation departs from the ridge center point, the impedance inverter model is no longer an exact description. However, it has been empirically found to agree quite well with the exact approach when the tripler is operating in

the high-efficiency regions of the contour plot. Therefore, the impedance inverter model is useful in predicting the frequency response of wide-band triplers which utilize a second harmonic idler circuit.

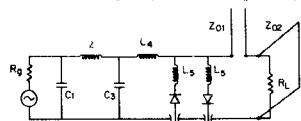

Using the impedance inverter model, a wide-band tripler was designed and constructed for operation at an input center frequency of 1.06 GHz. A balanced circuit was used to suppress the even harmonics and facilitate tuning of the second harmonic idler circuit. A circuit diagram of the tripler is shown in Fig. 3. Lumped elements  $C_1$ ,  $L_2$ ,  $C_3$  and  $L_4$ , which form a simple low-pass filter, are simulated by  $10\Omega$  and  $100\Omega$  transmission lines that are short compared to a wavelength at the input frequency. The inductors  $L_5$  are used to tune the second harmonic resonance. Transmission lines  $Z_{01}$  and  $Z_{02}$  are a quarter wavelength at the output frequency and form a two-section bandpass filter. A two-section, quarter-wavelength transformer is employed at the output so that the proper value of  $R_L$  is obtained. The bias voltage is supplied by a low-impedance source.

The approximate circuit values used in the experimental tripler are:

$$\begin{aligned}

C_1 &= 3.2 \text{ pF} & C_3 &= 5.0 \text{ pF} \\

L_2 &= 5.8 \text{ nH} & L_4 &= 3.0 \text{ nH} \\

R_L &= 20\Omega & R_g &= 50\Omega \\

L_5 &= 5.0 \text{ nH} \\

Z_{01} &= 80\Omega, \lambda/4 \text{ at } 4.2 \text{ GHz} \\

Z_{02} &= 50\Omega, \lambda/4 \text{ at } 3.3 \text{ GHz}

\end{aligned}$$

The diodes used were a matched pair of MA4748 diodes. The total capacitance of each diode was approximately 0.5 pF at -10V bias.

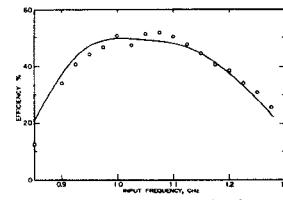

The performance predicted by the impedance inverter model is sensitive to small changes in the value of the time-average capacitance of the diode. Therefore, care must be taken to accurately determine the operating capacitance of the diode. For the capacitance of the diodes used in this tripler, the parasitic package elements introduced some uncertainty into the time-average value to be used. A value of  $C_0 = 0.9 \text{ pF}$  was chosen as a reasonable value. The impedance inverter parameters calculated from this value of  $C_0$  are  $K_1 = 71\Omega$  and  $K_2 = 43\Omega$ . The series resistance  $R_s$  was determined empirically to be 8 ohms by matching the experimental and theoretical midband efficiency. Figure 4 is a plot of the measured efficiency versus frequency for this tripler with an input power of 300 mW and a bias voltage of 7 volts. The multiplier has a midband efficiency of approximately 50% and an instantaneous bandwidth of 38%. The graph shows

both the experimental data and a curve based on the impedance inverter model. The agreement is considered good.

The second and fourth harmonic power output is down approximately 20 dB from the input signal. The fundamental power output is down 20 dB at the low end of the band, but it increases to approximately 12 dB down from the input power at the high end of the band.

In summary, a cascaded-impedance-inverter model of a charge-storage diode frequency tripler has been developed, and has been shown to be in agreement with the more exact model in predicting the frequency characteristics of a wide-band tripler. This circuit model should prove useful in the design of frequency triplers with bandwidths up to 50%, the bandwidth limitation on a balanced tripler because of harmonic interference.

#### References

1. J. C. Redd and K. L. Kotzebue, "Broadband high-efficiency tripler," *Electronics Letters*, vol. 6, no. 22, pp. 702-703, 29 October 1970.

2. C. B. Burckhardt, "Analysis of varactor frequency multipliers for arbitrary capacitance variation and drive level," *Bell Sys. Tech. J.*, vol. 44, no. 4, pp. 675-692, April 1965.

3. K. L. Kotzebue and G. L. Matthaei, "The design of broadband frequency doublers using charge-storage diodes," *IEEE Trans.*, vol. MTT-17, no. 12, pp. 1077-1086, December 1969.

4. D. H. Steinbrecher, "Efficiency limits for tuned harmonic multipliers with punch-through varactors," *Digest of Tech. Papers, 1967 International Solid-State Circuits Conference*, pp. 20-21, February 1967.

Fig. 1 Contour plot of optimum tripler efficiency as a function of phase angles  $\theta_2$  and  $\theta_3$ , for  $\theta_0 = 0$  and  $Q = 40$ . For clarity, the complete plot is not shown; efficiency is periodic in  $\theta_2$  and  $\theta_3$ .

Fig. 2 Cascaded-impedance-inverter model of a frequency tripler with second harmonic idler circuit.

Fig. 3 Circuit diagram of experimental wide-band tripler.

Fig. 4 Theoretical curve of efficiency as a function of frequency, together with experimental points.

# Notes

**AMERICAN ELECTRONIC LABORATORIES, INC.**

P.O. BOX 552 LANSDALE, PA. 19446

**BASIC SEMICOND. RESEARCH THRU DEVELOP'T OF SOLID STATE & MW DEVICES, ANT. SYSTEMS - COMMUNIC. EQUIP. - DEVELOP, DESIGN & PROGRAM MANAGE COMPLEX MILITARY & COMMERCIAL SYSTEMS**

**STANFORD RESEARCH INSTITUTE**

MENLO PARK, CALIFORNIA 94025

**R&D IN: MICROWAVE CIRCUITS, ANTENNAS, SYSTEMS, SOLID-STATE & ACOUSTIC DEVICES. PLASMA PHENOMENA, LASERS IN MEDICINE, METEOROLOGY, OCEANOGRAPHY**